組合邏輯電路的設計就是將實際的,有因果關系的問題用一個較合理、經濟、可靠的邏輯電路來實現。一般來說在保證速度、穩定、可靠的邏輯正確的情況下,盡可能使用最少的器件,降低成本是邏輯設計者的任務。本文將組合邏輯電路的設計的實例引入到EDA中,進一步將電子設計自動化EDA(Electronic Design Automation)應用于數字電子技術教學中,而Multisim9軟件是一個專門用于電子線路仿真與設計的EDA工具軟件,為該課程的教學和學習打下一個良好的基礎。

1 Multisim9軟件及其特點

Multisim9軟件是加拿大IIT公司在推出EWB基礎上的一款更新、更高版本的電路計與仿真軟件,可以對模擬、數字和混合電路進行電路性能仿真和分析,作為一個高度互動且易于使用的工具,它可以幫助學生深刻理解電路理論與行為。

①直觀的圖形界面:整個操作界面就像一個電子實驗工作臺,繪制電路所需的元器件和仿真所需的測試儀器均可直接拖放到屏幕上,輕點鼠標可用導線將它們連接起來,軟件儀器的控制面板和操作方式都與實物相似,測量數據、波形和特性曲線如同在真實儀器上看到的一樣。②豐富的元器件庫:Multisim9大大擴充了EWB的元器件庫,包括基本元件、半導體器件、運算放大器、TTL和CMOS數字IC、DAC、ADC及其他各種部件,且用戶可通過元件編輯器自行創建或修改所需元件模型。③強大的虛擬儀器功能。為用戶提供多種虛擬測儀器,虛擬測試儀器的面板與實際儀器相似,在平臺上可隨時調用各種儀器對電路進測試、分析;能直接顯示有關數據或波形,具有數據存儲功能。

2 組合邏輯電路設計在EDA技術中的應用

2.1 組合邏輯電路設計過程組合邏輯電路在邏輯功能上的特點是:這種電路在任何時刻的輸出僅僅取決于該時刻的輸入信號,而與這一時刻輸入信號作用前電路原來的狀態沒有任何關系。其電路結構基本上由邏輯門電路組成,只有從輸入到輸出的通路,沒有從輸出反饋到輸入的回路,這類電路沒有記憶功能。組合邏輯電路設計的一般過程是:①分析事件的因果關系,并用二值邏輯的0與1列出真值表。②把真值表轉換為對應的邏輯函數。③根據電路的具體要求和器件的資源情況等因素選定器件的類型。④將邏輯函數化簡或變換成與所選用的器件類型相一致。⑤根據化簡或變換后的邏輯函數,畫出邏輯電路圖。⑥根據邏輯電路圖,用選定的器件實現具體的電路裝置,并進行調試完成。

邏輯化簡是組合邏輯電路設計的關鍵步驟之一。但最簡設計不一定是最佳的,一般情況在保證速度,穩定可靠與邏輯關系清晰的前提下,應盡量使用最少的器件,以降低成本,減少體積。

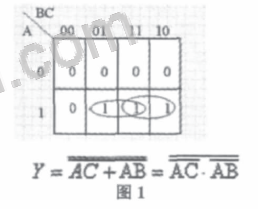

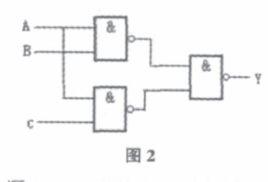

2.2 應用舉例①舉重裁判判決電路。A、B、C三個舉重裁判對運動員成績判決,其中A為主裁,具有否決權。當兩個以上裁判認可時(須含有主裁),運動員成績有效,用與非門實現。分析設計要求,列出真值表。設A、B、C三個裁判對運動員成績進行判決,同意用1表示,不同意用0表示,Y為表決結果,同意用1表示,不同意用0表示,同時還應考慮A為主裁,具有否決權。②由真值表寫出邏輯表達式Y=ABC+ABC+ABC。③由卡諾圖化簡后,變換為與非表達式。④根據輸出邏輯函數畫邏輯圖。

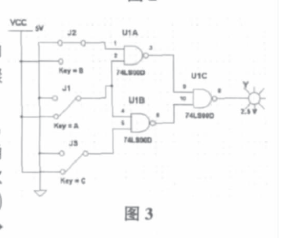

2.3 測試電路創建本文中的電路測設電路圖3所示,具體步驟如下:

①在元器件庫中單擊Sources,列表中選中VCC,單擊OK按鈕確認取出電源5V。②其他元器件依次類推,可參照以下說明使用。1)UIA、UIB、UIC與非門在TTL74LS→中選擇74LSOON。2)J1、J2、J3開關在Electro_Mechanical→Component Browser→SPDT_SB0 3)X1指示燈在Indicators→中選擇PROBE_DIC_RED。

2.4 測試方法說明及結果觀察啟動Multisim的仿真開關后,將開關分別設置為key=B、key=A、key=C,同時右邊輸出指示燈設置為Y,根據鍵盤字母的敲擊,Y指示燈開始變化,從000至111循環顯示,本例顯示的是當ABC=91時,判決結果正確,指示燈Y照亮,剩下的情況以此類推。

綜上所述,組合邏輯電路設計的例子很多,只有在不斷設計中才能找到學習的樂趣,通過EDA軟件的使用,切實感受到了EDA軟件功能的強大,為我們設計出更多更好的組合邏輯電路實例打下了堅實的基礎,更進一步加深了EDA軟件在教學中的應用,為我們在電子電路的讀圖及分析電子電路的能力方面帶來了幫助。

(審核編輯: 智匯張瑜)

分享