1 引言

數據采集很多時候需要將數據傳輸到遠程計算機,也有些采集系統有很多采集點,比如火災傳感器,這就需要數據傳輸部分能夠方便地組網。在短距離內USB傳輸和1394火線傳輸都是一個較為理想的方法,但涉及到遠距離傳輸和組網時,它們就不是那么方便了。所以很多時候通過以太網傳輸采集到的數據是一種較好的方式。目前設備實現聯網的做法一般是使用CPU運行操作系統,由操作系統里的軟件協議棧完成對TCP/IP協議的處理。這種方式需要編寫CPU與數據采集部分接口的驅動和網絡通訊的傳輸軟件,開發工作量較大,設計較為復雜。并且CPU在產生接口時序方面較為不便,很多時候需要用FPGA+CPU的方式:FPGA完成與數據采集部分接口時序的產生和數據的緩存,CPU完成數據傳輸。因為數據采集系統中經常會使用FPGA,如果能用FPGA和少量易用的外圍器件實現網絡傳輸則是一種較為理想的方式。我們設計了一個網絡傳輸平臺,主要包括FPGA、DDR芯片和硬件化的網絡協議棧芯片,可以通過以太網和計算機通訊,將數據傳輸到計算機中。

2 平臺結構

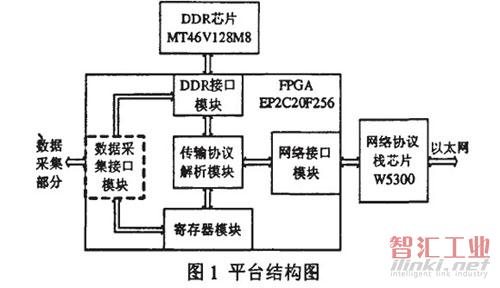

平臺結構包括硬件上的結構和FPGA邏輯結構。其結構如圖1所示。其中數據采集模塊是數據采集系統的傳輸平臺需要的一個模塊,但是目前沒有,可以根據實際需要進行開發。

2.1 硬件結構

平臺主要包括三個部分:FPGA,DDR存儲芯片和網絡協議棧芯片。FPGA為平臺的主控芯片,使用Alter Cyclone II EP2C20F256,該FPGA具有1 8,752個LE,239,616位存儲器空間,26個嵌入式乘法器,4個PLL,152個用戶可用管腳,封裝采用256腳F‘meline BGA,體積較小。

DDR存儲芯片使用MICRON M’r46V128M8—6T,容量128MB,數據線寬度為8bit,該容量是DDR單片芯片中容量最大的。芯片最高可工作在167MHz。使用DDR對布板有較高的要求,我們在布板時考慮到了過孔和焊盤長度對走線長度的影響,保證了對同一組數據線和時鐘的精確等長布線。通過估計信號的回流路徑進行走線和參考平面分割,以保證信號回路阻抗的連續性,減小信號之間的串擾。選擇了適當的線寬、疊層方式及疊層厚度,使得單端走線的阻抗控制在50歐姆,差分走線阻抗在100歐姆,以確保傳輸線的阻抗匹配。這些措施保證了良好的信號的完整性,提高了時序余度,降低了對DDR IPCore的時間參數精確性的要求,為平臺的穩定運行打下了基礎。

網絡協議棧芯片使用的是WIZNET W5300,芯片內部集成了以太網物理層(PHY)、802.3以太網MAC和TCP/IP協議棧。該芯片可用在10M/100M以太網中,完成ISO七層模型中的物理層、數據鏈路層、網絡層和數據傳輸層的任務,將控制器從復雜的網絡協議處理中解脫出來,提供了一個易于實現的網絡傳輸方式。

因此我們選取了并行接口,工作在直接尋址模式。

2.2 FPGA邏輯結構

在進行FPGA邏輯編寫時采用了模塊化設計,結構主要包括四個部分:DDR接口模塊、網絡接口模塊、傳輸協議解析模塊和寄存器模塊。DDR接口模塊對DDR芯片進行上電初始化,產生DDR的讀寫時序并控制DDR刷新。網絡接口模塊對網絡協議棧芯片進行上電初始化,產生芯片的讀寫時序,并控制芯片發送和接受數據。傳輸協議解析模塊對網絡接口模塊送來的數據進行解析,轉換成對DDR或寄存器的讀寫操作,并將DDR模塊或寄存器模塊讀出的數據送給網絡接口模塊,通過網口發送出去。寄存器模塊包括16個16位的寄存器,存放參數設定和狀態信息,遠程用戶通過讀寫寄存器實現對數據采集的控制。

在進行FPGA邏輯編寫時采用了層次化的設計。每層完成其特定工作,使得設計清晰明了。系統的層次結構如圖2所示。

從整體上來看,平臺結構分為設備層、接口層和控制層。設備層為FPGA外圍芯片,接口層作為設備層和控制層的橋梁,面向設備發送相應指令,產生特定時序的信號;面向控制層提供數據。

控制層將接口層送來的數據進行解析,轉化成對接口層的操作,控制整個平臺的工作。在網絡接口模塊中,同樣也可分為接口層和控制層。接口層將上層所有對W5300訪問的操作按照其時序要求產生相應地信號,控制層則控制w5300芯片完成以太網通信。

2.2.1 DDR接口模塊

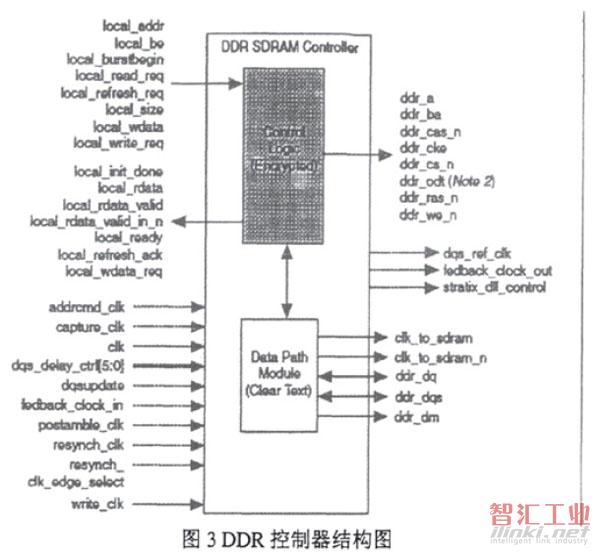

DDR接口使用Altera提供的IPcore。該IPcore包括控制邏輯和數據通道兩部分,如圖3所示。

控制邏輯面向DDR芯片執行總線的操作,對內提供一個簡單的接口。數據通道在內部讀寫數據總線與DDR芯片的雙向數據總線之間提供一個接口,因為DDR芯片的數據總線是上升下降沿都傳送數據,內部總線僅在上升沿傳送數據。所以內部數據總線寬度是DDR芯片數據總線的兩倍。本設計中內部總線的寬度為16位。DDR突發數據傳輸長度選擇2。

FPGA邏輯巾還包括一個隨機數Ⅻ4試模塊。可以產生偽隨機數寫入DDR芯片。然后將其讀出。

通過比較兩者是否相同,可毗判斷芯片的好壞。隨機數Ⅻ5試在上電時會執行一次。執行結果由扳子上LED燈指示。

2.2 2 時絡接口模塊

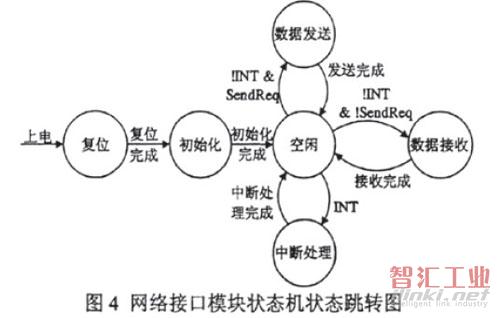

網絡接口模塊丹為控制層和接口層。控制層由多個處理模塊組成,包括:復位模塊、初始化模塊、數據接收模塊、數據發送模塊和中斷處理模塊,每個模塊完成一種情況的處理。這些模塊受一十狀態機的控制,狀志機根據不同的話分別執行相應的模塊。狀態機的跳轉如圖4所示:

系統上電開始,狀態機進入復位W5300狀態。在其復位管腳上產生一個2微秒的負脈沖以復位芯片。復位完成后進八初始化階段。初始化階段設置芯片工作方式、平臺網絡接口的MAC地址、源口地址、源端口號、掩碼、同蓑和協議類型等。車系統采用的是直接尋址方式,協議婁型選擇UDp。初始化完成后狀態機進人空用狀態。在這個狀態下,先檢測是否有中斷㈣產生。如果有中斷則進入中斷處理狀態,執行中斷處理模塊,如果沒有中斷則檢剁是否有發送數據請求(SendReq)。

如果有則進入數據技逆狀志,執行數據發送模塊。如果既沒有中斷也投有菱送數據請求。則進入數據接收狀態,執行數據接收模塊。數據接收模塊執行時。首先要讀取W5300內部的接收數據字節長度寄存器。如果不為0表明W5300接啦到數據,則讀取數據,否則直接結束數據接收過程,狀態機返到空閑狀態。

2.2.3 協議解析模塊

網絡接口模塊從W5300中讀取到數據后,將數據發送到協議解析模塊。協議解析模塊根據這些數據解析出相應的操作,讀寫寄存器或DDR存儲器。因為數據寫入寄存器只需要一個時鐘周期,所以寫入寄存器的數據可以被即時寫入。而DDR有突發數據傳輸長度的限制和刷新的存在,使得數據無法即時寫入。因此寫入DDR的數據先緩存在一個寫入FIFO中,當該FIFO中的數據大于突發數據傳輸長度時,向DDR接口模塊請求一次數據寫入。讀取數據時,因為讀寄存器和DDR的速度遠大于網絡的傳輸速度,因此讀取的數據需要存放在讀出FIFO中。讀取DDR時,采用了預讀方式,持續讀取DDR直到讀出FIFO滿,但實際發送的數據個數仍然為實際需要的數據量,這種方式降低了對DDR讀取的復雜度。

3 傳輸協議設計

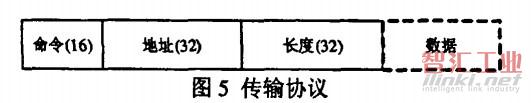

我們定義了一個傳輸協議如圖5所示。協議包括16位命令、32位地址、32位長度和可選的數據部分。命令表示本次操作要完成的任務,目前定義了四個,分別是:CMD_RD_REG(讀寄存器)、CMD_WD_REG(寫寄存器)、CMD_RD_MEM(讀DDR存儲器)、CMD_RD_MEM(寫DDR存儲器)。地址表示本次操作的起始位置,長度表示本次操作的數據長度。數據是可選部分, 當命令字段為CMD WD_REG或CMDWD_MEM時,表明本次為寫操作,此時有數據部分,長度為長度字段值,平臺將把該數據寫入到寄存器或DDR存儲器指定的地址位置;當命令字段為CMD_RD REG或CMD_RD_MEM時,表明本次為讀操作,此時沒有數據部分,平臺將從寄存器或DDR存儲器指定的地址讀取指定的長度數據發送至遠程計算機。

以一個常見的數據采集過程說明使用本協議是如何工作的。遠程軟件以本平臺P地址和端口號為源m地址和源端口號向本平臺發送一個寫寄存器命令,將寄存器模塊中控制寄存器的開始工作位寫l,該位為l則觸發數據采集接口模塊開始工作,其首先要對DDR存儲器清零,然后等待外部數據的到來,將數據存儲在DDR存儲器中,存儲完畢后將寄存器模塊中表示狀態的寄存器的數據記錄完成指示位置l。遠程軟件發出開始工作指令后應一直發送讀取寄存器命令,讀取該位直到其為l。然后發送讀DDR存儲器命令,地址為當前待讀取數據的地址,長度選取合適的數值,從DDR中讀取數據。讀取一段數據后將地址加上長度值讀取下一段數據,直到數據讀取完成。

從上可以看到遠程軟件需要一直讀取狀態寄存器以確定平臺工作狀態,占用較多的計算機CPU時間,同時占用了網絡帶寬,在多個本平臺的存在下,這種情況更加明顯。這在多用戶的以太網環境里是不允許的。因此我們的平臺采用了消息機制,通過這種機制可以避免以上問題。

我們將寄存器模塊的第一個寄存器作為消息寄存器,當該寄存器非零時,協議解析模塊將把該寄存器的值發送到遠程軟件,發送頻率每秒一次,直到該寄存器被清零。在以上舉例的數據傳輸過程中,遠程軟件發出開始工作指令后即可進入等待狀態,數據采集接口模塊在數據記錄完成后將消息寄存器某位置l,平臺然后開始發送消息寄存器值。軟件接收到該寄存器值后,先發送寫寄存器命令將該寄存器清零,然后根據消息值進行相應的操作。消息寄存器為16位,因此最多可以定義16種消息。

4 測試結果

我們將一臺計算機和平臺通過交叉線連接起來,設定好雙方的m地址后,在計算機上通過軟件向平臺上的DDR讀寫數據來測試平臺的數據傳輸速度。寫入時使用的協議長度字段為1462,讀取時為1472,這樣發送的數據長度或讀取的數據長度加上UDP首部的長度為1500,是以太網的最大傳輸單元(MTU)的長度。在這種情況下測得平臺接收數據速率在70Mbps,發送數據速率達到了30Mbps。

5 結論

我們設計了一個網絡傳輸平臺,使用FPGA控制硬件化的TCP/IP協議棧芯片來完成網絡傳輸,避免了由于使用CPU帶來的一些問題,同時平臺具有大容量的存儲器,剩余豐富的Io管腳,在平臺基礎上再進行少量的開發即可實際使用。我們采用了模塊化的設計和層次化的結構。使得平臺結構清晰。設計了自定義的傳輸協議,針對實際環境進行了優化。經測試平臺達到了較高的傳輸速度,其接收數據速率達到了70Mbps,發送數據速率達到了30Mbl硌。本平臺具有設計簡潔、靈活可靠、性能突出等優點,適合數據采集系統中的數據傳輸的應用。(作者:章濤,王永綱,陳俊,都軍偉)

(審核編輯: 智匯小新)

分享